Blink_LED Converted to VHDL by ChatGPT

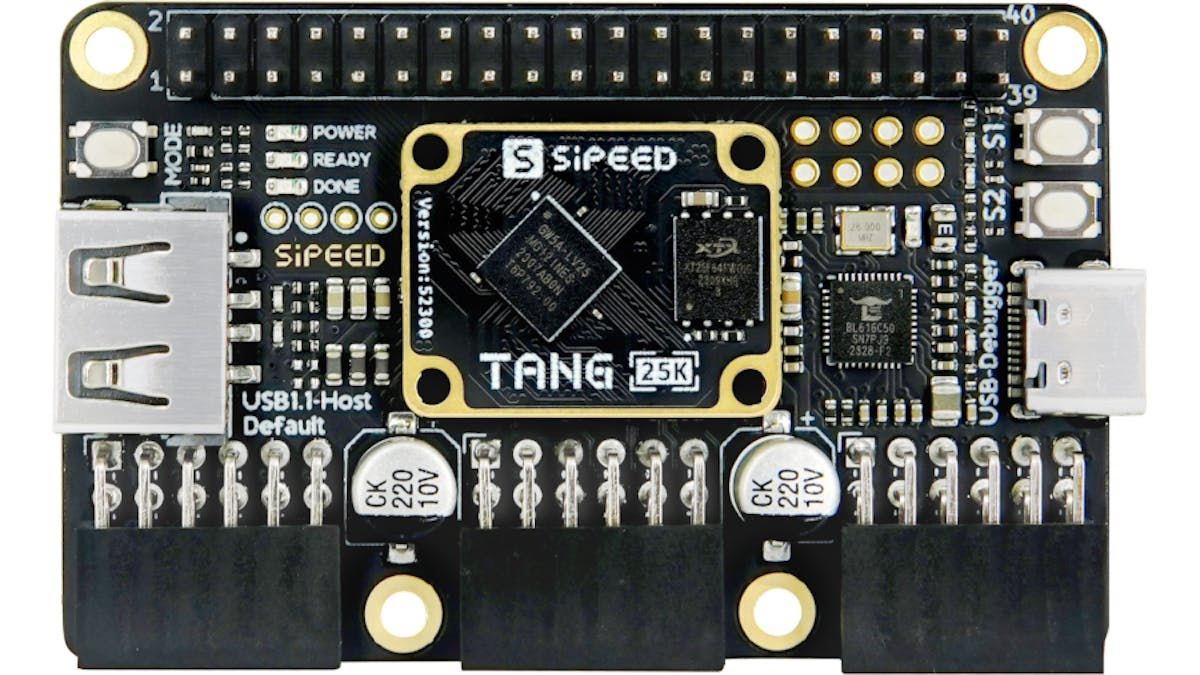

I used ChatGPT to convert Verilog file Blink_LED.v mentioned in my Sipeed Tang Nano 20K post to VHDL - see the post. It compiled OK but the resultant netlist wouldn't place and route with the Verilog constraints files. All I had to do was change 'clk' to ''sys_clk' in both files. I don't know why ChatGPT changed 'clk' to 'sys_clk' when it generated the VHDL. I thought that clk might be a reserved word in VHDL but ChatGPT said it wasn't!

The chip programmed OK with the bitstream (probably the same as the Verilog one) and the LED is flashing at the same rate.

I don't know how well ChatGPT will cope with larger programs.

Comments

Post a Comment