Sipeed Tang Nano 4K FPGA module

I've been playing with this incredibly cheap (£12) FPGA module from Sipeed in China:

https://www.gowinsemi.com/en/support/devkits_detail/39/

I've provided this link as it's a lot more informative than Sipeed's description. You'll need to scroll down.

You can buy the modules, as well as ones with larger chips and different facilities, via AliExpress:

https://a.aliexpress.com/_EHg7VcF

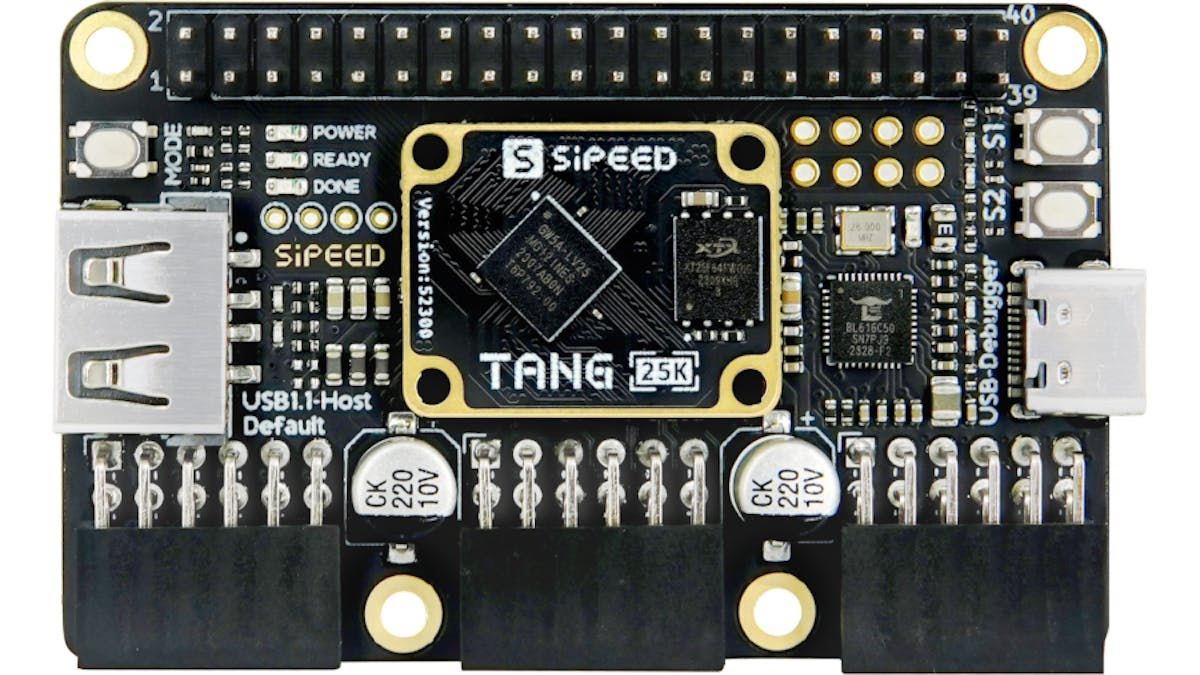

Here is a nice pic of the module with the pin connections. They now supply an OP2640 2 MP camera plugged into the camera connector.

It uses the Gowin Semi GW1NSR-V4CQN48PC 4K device. The free Gowin Educational EDA tools work very well with it - both Verilog and VHDL may be used. I prefer VHDL and have found that ChatGPT does a very good job of converting Verilog code to VHDL, if you ask it nicely. 8)

Download the EDA from here:

https://www.gowinsemi.com/en/support/home/

You will need to register and login.

BTW, the FPGA incorporates an Arm Cortex-M3 hard core.

Several Verilog samples showing how to use the module are available on GitHub:

https://github.com/sipeed/TangNano-4K-example

Here's one of those examples converted to VHDL:

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.STD_LOGIC_ARITH.ALL;

use IEEE.STD_LOGIC_UNSIGNED.ALL;

entity LED_Toggle is

Port ( clk : in STD_LOGIC;

led : out STD_LOGIC);

end LED_Toggle;

architecture Behavioral of LED_Toggle is

signal counter : INTEGER := 0;

signal clk_div : STD_LOGIC := '0';

-- Assuming a 27 MHz clock

constant CLOCK_FREQ : INTEGER := 27000000;

constant TOGGLE_FREQ : INTEGER := 1;

constant MAX_COUNT : INTEGER := CLOCK_FREQ / (2 * TOGGLE_FREQ);

begin

process(clk)

begin

if rising_edge(clk) then

if counter = MAX_COUNT then

counter <= 0;

clk_div <= NOT clk_div;

else

counter <= counter + 1;

end if;

end if;

end process;

led <= clk_div;

end Behavioral;

Call it Blink.vhd

You'll need a physical constraints file which associates clk and led to the actual pins on the FPGA. File should contain

IO_LOC "led" 10;

IO_LOC "clk" 45;

IO_PORT "clk" IO_TYPE=LVCMOS33 PULL_MODE=UP;

Call the file Blink.cst

Most designs require a timing constraints file but it isn't needed for this example.

Comments

Post a Comment