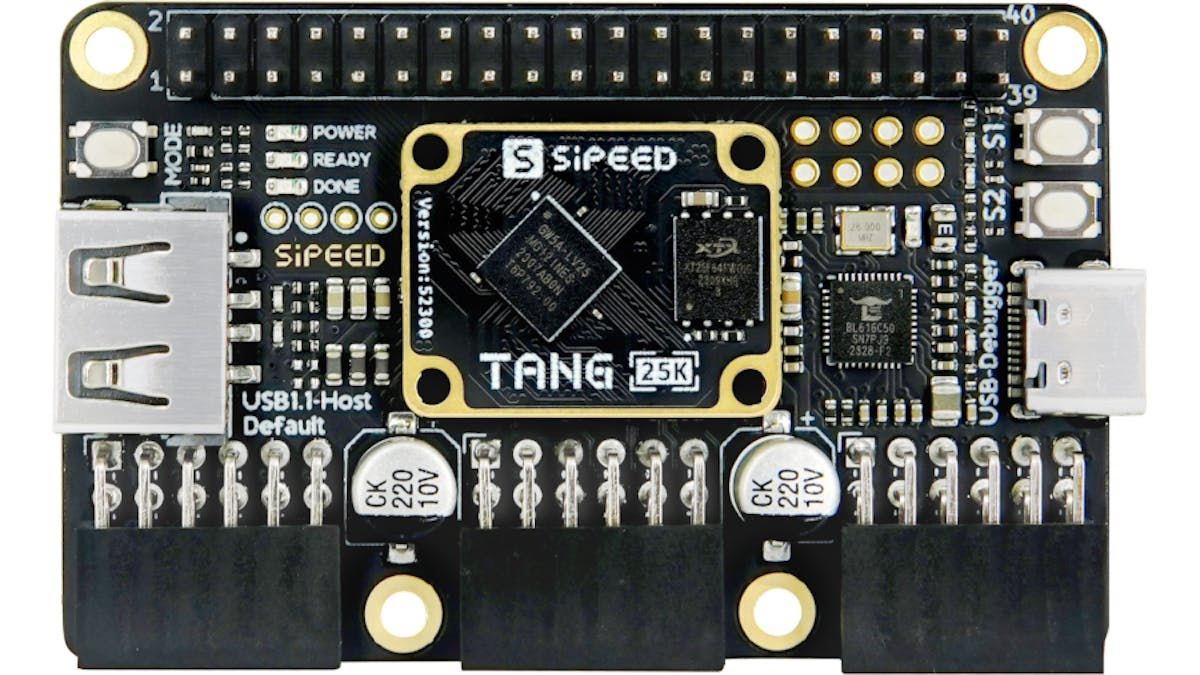

Sipeed Tang Nano 20K FPGA board

Sipeed in China produces a range of little low-cost DIL modules using Gowin FPGAs. They are available via AliExpress. The 20K costs about £26 and contains a GW2AR-18 QN88 device: https://wiki.sipeed.com/hardware/en/tang/tang-nano-20k/nano-20k.html I ordered one about a week ago and it was delivered by Evri this morning. I connected it to my laptop using the supplied USB cable and the orange LEDs lit up in sequence continuously indicating that it was working. I downloaded a Verilog file which simply blinked one LED at 1 Hz, the associated physical constraints file and the timing constraints file. The Verilog is compiled to produce a netlist that is placed and routed, generating a bitstream that is downloaded into the chip. Here's the Verilog file (Blink_LED.v): module led ( input sys_clk, input sys_rst_n, // reset input output reg led ...